C'è una roadmap HBM fino al 2038: i dettagli dalle memorie HBM4 alle HBM8

KAIST mappa l’evoluzione della memoria HBM: da 2 TB/s a 64 TB/s, con NAND on-die e package bumpless, rivoluzionando AI e HPC.

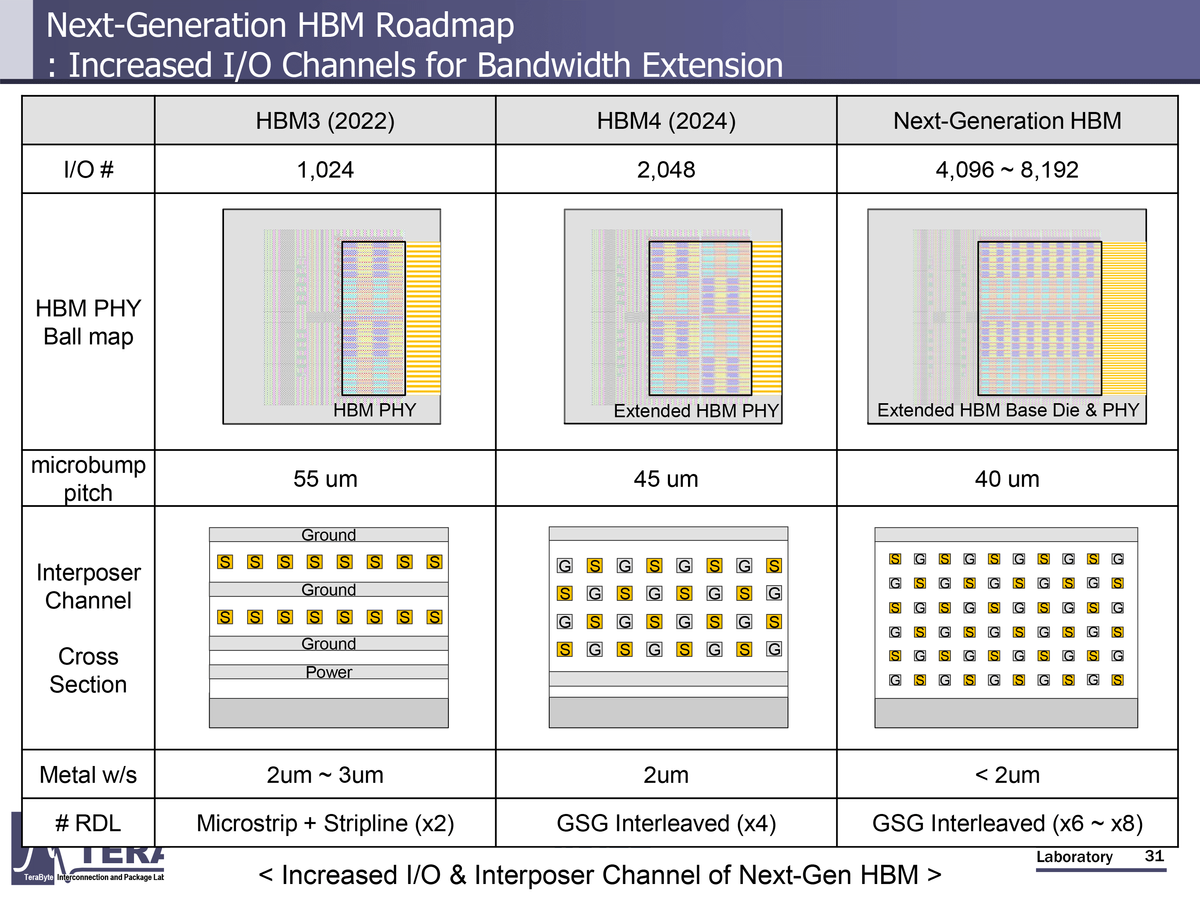

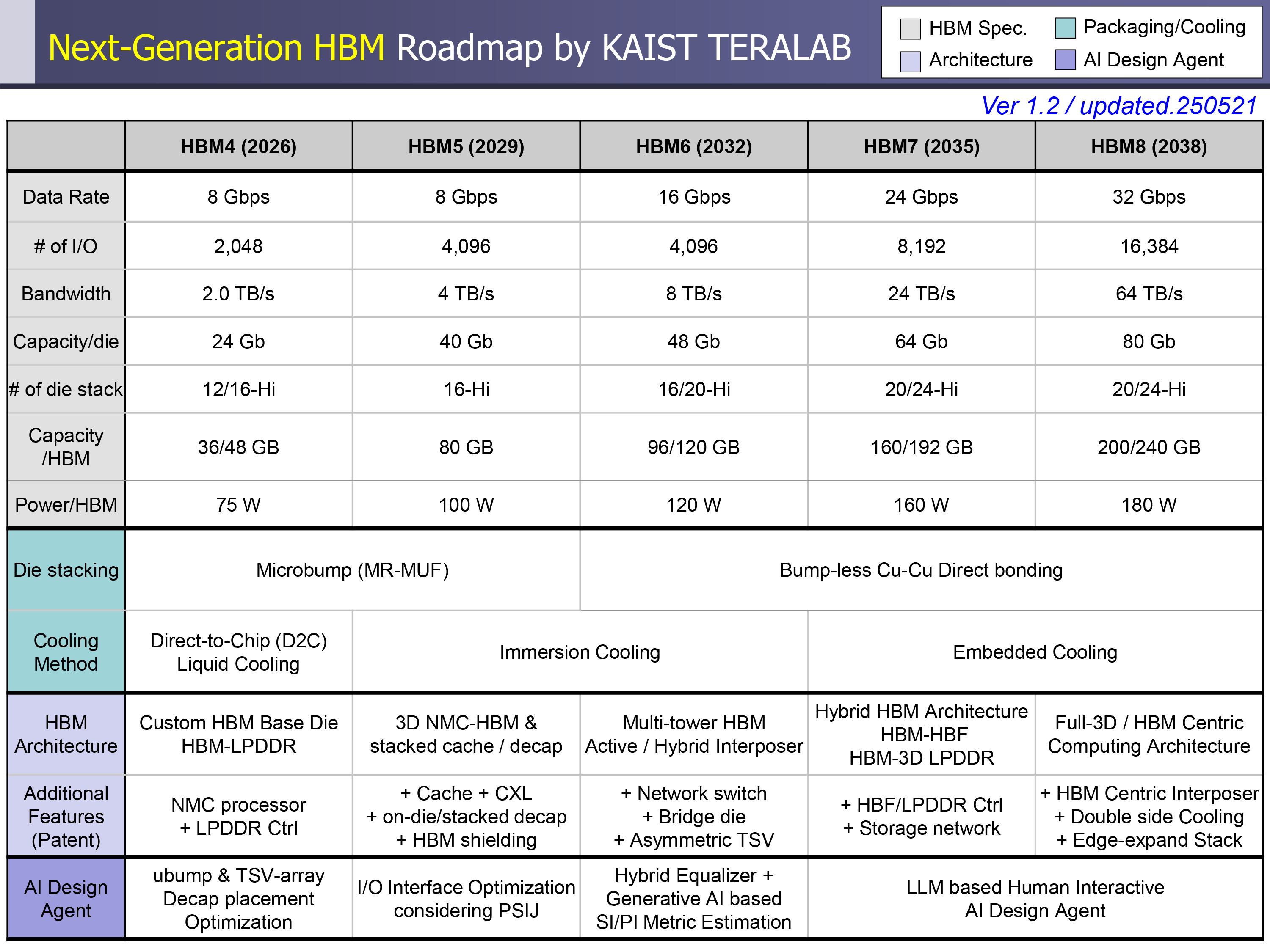

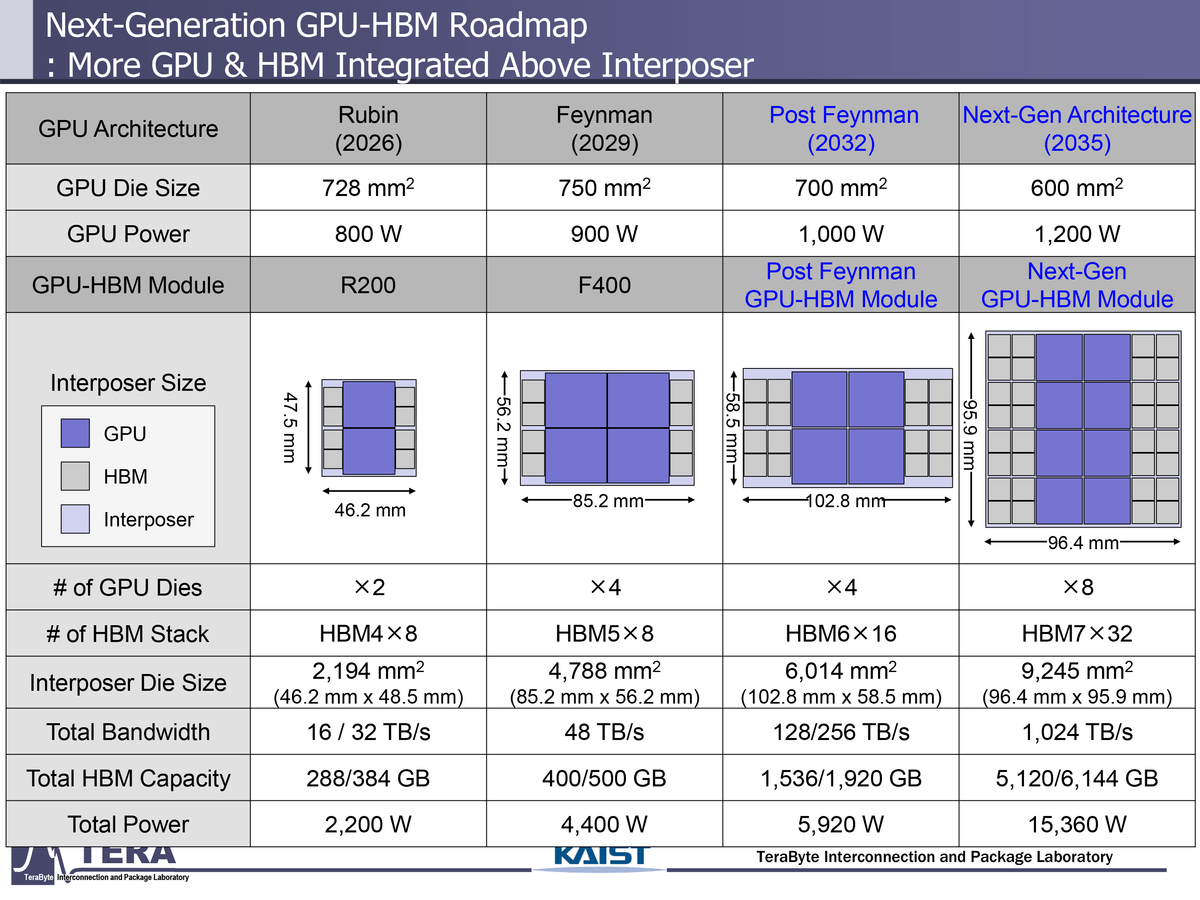

Il laboratorio KAIST ha pubblicato un white paper di 371 pagine che delinea l’evoluzione della High-Bandwidth Memory (HBM) fino al 2038: la banda crescerà da 2 TB/s a 64 TB/s per stack, mentre l’I/O passerà dagli attuali 1.024 bit a 16.384 bit, spingendo i pacchetti HBM a potenze di picco di 180 W per singolo stack. Si tratta della prima roadmap organica che integra anche l’uso dell'IA per l’ottimizzazione fisica e termica dei layout.

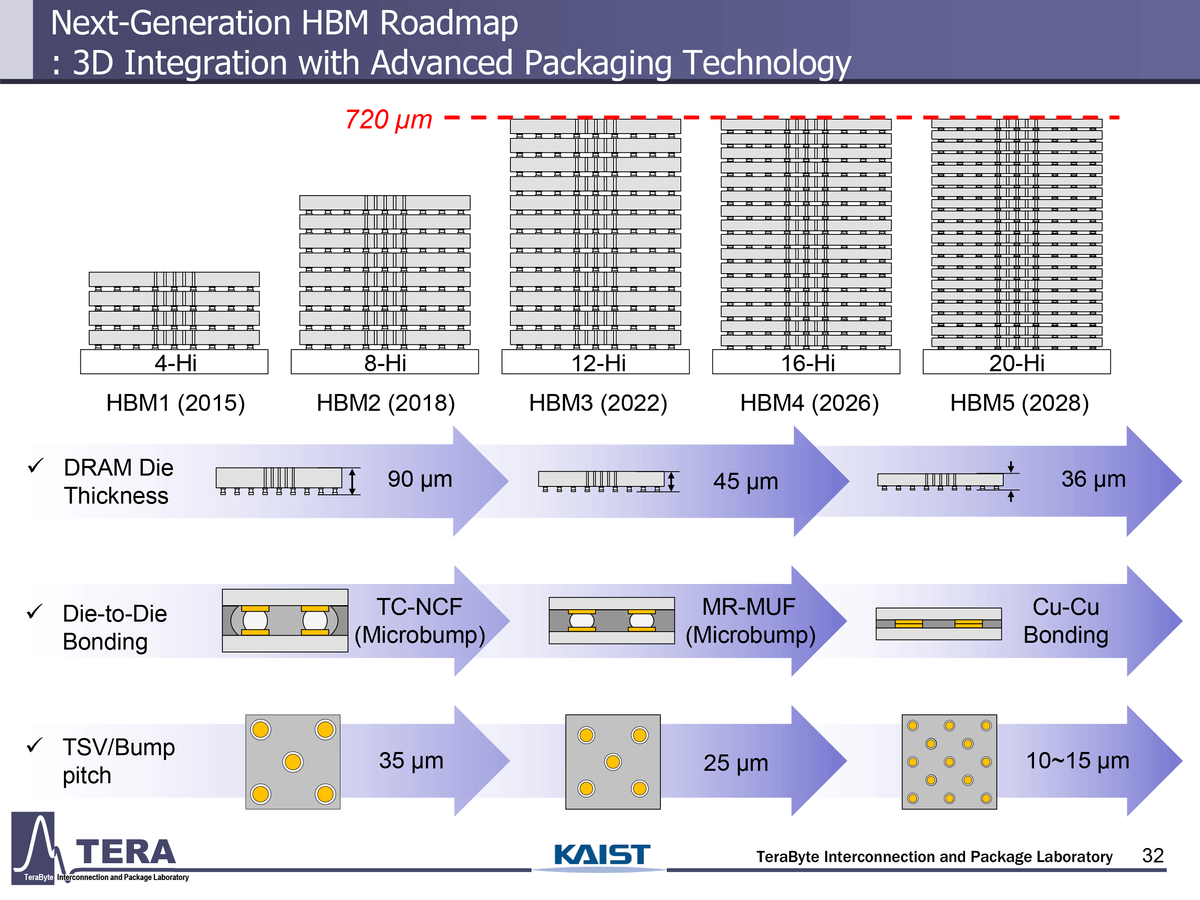

L'HBM4 arriverà sul mercato nel 2026 con velocità fino a 8 GT/s su bus a 2.048 bit, per 2 TB/s di throughput e capacità di 36-64 GB per stack. Micron ha già spedito i primi sample da 36 GB a clienti AI e HPC, annunciando un’efficienza energetica superiore del 20% rispetto all'HBM3E. Dal lato industriale, JEDEC ha ratificato la specifica JESD238, introducendo 32 canali indipendenti per stack e opzioni di tensione flessibili per migliorare la resa termica. Nel 2029 debutterà l'HBM5, che raddoppierà l’I/O a 4.096 bit mantenendo 8 GT/s, per 4 TB/s a 100 W di consumo; KAIST prevede l’integrazione di cache L3 on-die e bus CXL per collegare la DRAM esterna. Samsung adotterà l'hybrid bonding per questa generazione, eliminando i microbump e riducendo la resistenza di interconnessione, mentre SK Hynix valuta ancora varianti MR-MUF avanzate.

L'HBM6 (2032) alzerà la velocità a 16 GT/s e la banda a 8 TB/s, con stack da 120 GB e consumo di 120 W; sarà la prima generazione a sfruttare il bonding “bumpless” rame-rame e interposer ibridi silicio-vetro. Intel, dal canto suo, ha presentato EMIB-T, un’architettura di packaging con TSV verticali che garantisce alimentazione a bassa impedenza e supporto nativo a HBM4/4E, preparando il terreno per integrazioni future. Con l'HBM7 (2035) si passerà a 24 GT/s e a un bus da 8.192 bit (24 TB/s), mentre l'HBM8 chiuderà il ciclo nel 2038: con memorie a 32 GT/s, bus da 16.384 bit, banda di 64 TB/s e stack da 200-240 GB. Cruciale l’introduzione dell’architettura HBF – High-Bandwidth Flash, che porta le NAND sul base-die per spostare i dati dallo storage all’HPC senza passaggi sul bus host. Le proiezioni indicano acceleratori AI da 15 kW capaci di ospitare più di un terabyte/s di banda complessiva.

L’impatto industriale sarà duplice: da un lato, le interfacce ultra-larghe richiederanno raffreddamento a liquido integrato nei package e materiali a bassa resistività; dall’altro, l’esplosione dei consumi spingerà lo sviluppo di packaging co-design chip-rack per data centre di prossima generazione. La convergenza fra DRAM e flash ad altissima banda promette di ridurre la latenza, ma solleva nuove sfide di sostenibilità energetica che l’ecosistema dovrà affrontare entro il prossimo decennio.

Fonte: Tom's Hardware